## ET4000/W32i Graphics Accelerator Data Book

© Copyright Tseng Labs, Inc. 1993

**■** 9006165 0000099 T93 |

## TSENG LABS ET4000/W32i DATA BOOK ERRATA

Release Date: 10/1/93

#### 10/1/93

Section 2.11.6.3 has been changed to the following:

#### 2.11.6.3 Color Expansion and Font Painting

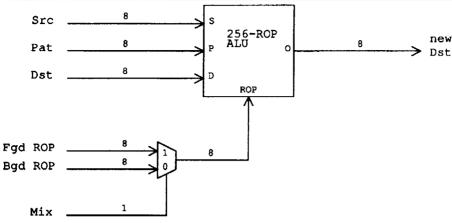

The accelerator is capable of expanding a 1 bit-per-pixel (monochrome) pixel map into an 8 bit-per-pixel map. This is a very common operation when painting fonts. Opaque text (that is, text of a solid foreground color painted with a solid background color) is drawn by setting the Foreground ROP to "Src," and the Background ROP to "Pat," and supplying the 1 bit-per-pixel map as the Mix Map. A "0" in the Mix Map will result in the fixed color in the Pattern map to be written to the Destination, and a "1" in the MixMap will draw the Source color into the Destination. Of course, there is no restriction that the Pattern and Source Maps be solid color; they could just as easily be 2-dimensional pixel maps. The important point to understand is how the 1-bit-per-pixel Mix Map is used to select between the programmed Foreground and Background ROP's.

A similar approach is used to draw transparent text (that is, text of a solid foreground color painted such that the Destination Map shows through in the background). It is a simple matter of setting the Foreground ROP to "Src", and the Background ROP to "Dst." Of course, it is also possible to make the Foreground ROP and Background ROP functions of any of the three pixel maps to obtain the desired result.

If the programmer wishes to operate as if the pixel maps are 16, 24, or 32-bits-per-pixel, each bit of the Mix Map must be replicated 2, 3, or 4 times, respectively, because the accelerator ALWAYS expands one BIT of the Mix Map to one BYTE of the other maps.

#### 10/1/93

The following sections, 2.11.6.5 and 2.11.6.6, have been added:

#### 2.12.8.6 Bit Masking

A common graphics operation involves the use of a bit-oriented mask to control whether certain bits of the Destination data are operated on or not. An example of this is the standard VGA "Bit Mask" Register (GDC Indexed Register 8).

A bit value of 0 in the mask leaves the corresponding bit of the Destination data unchanged, and a bit value of 1 causes that bit of the Destination data to take on some value, which could be constant, or a function of Source and/or Destination data.

This type of operation is easily accomplished with the accelerator by using the Pattern Map to hold the desired Bit Mask value, and setting the Pattern X/Y Wrap to 4-by-1. Then the Foreground ROP can be chosen properly so that a bit value of 0 in the Pattern Map applies a certain 2-operand ROP to that Destination bit, and a bit value of 1 in the Pattern Map applies another 2-operand ROP to that Destination bit. The table below summarizes the resultant Destination bit value ("Dst<n>") when various Foreground ROP's are applied:

| <u>ROP</u> | Pat < n > == 0 | Pat < n > == 1               |

|------------|----------------|------------------------------|

| CA         | unchanged      | Src <n></n>                  |

| AC         | Src <n></n>    | unchanged                    |

| FA         | unchanged      | 1                            |

| 0A         | unchanged      | 0                            |

| 8A         | unchanged      | Src <n> &amp; Dst<n></n></n> |

| EA         | unchanged      | Src <n>   Dst<n></n></n>     |

| 6A         | unchanged      | Src <n> XOR Dst<n></n></n>   |

| 9 A        | unchanged      | Src <n> XNOR Dst<n></n></n>  |

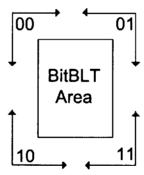

### 2.12.8.7 Compound BitBLT's

Some types of graphics operations require a complex combination of Pixel Maps. In these cases, it makes sense to perform the operation as two separate BitBLT's, or a "compound BitBLT." It is recommended, however, that the problem be thoroughly analyzed before deciding to use a compound BitBLT since in many cases the solution is subtle and may not be immediately apparent (such as the Bit Masking described in the previous section).

The following example is just one case of applying compound BitBLT's:

Consider a situation that has memory organized as one byte per pixel (and displayed as one byte per pixel), but each byte is broken into 2 nibbles, such that two different processes share the one byte, with each process appearing to have 4-bits per pixel.

One process would use a BitMask of 00001111, and the other uses a BitMask of 11110000. Now, in order to perform a BitBLT that uses the MixMap (stored in system memory) to select between a Foreground Color and a Background Color, the following two BitBLT's would be performed:

#### BitBLT #1

- 1. Program Data Routing to take MixMap data from the host.

- 2. Write Foreground Color to off-screen memory (replicated to fill a doubleword).

- 3. Write Background Color to off-screen memory (replicated to fill a doubleword).

- 4. Load Source Address Register with off-screen address where Foreground Color was stored.

- 5. Load Pattern Address Register with off-screen address where Background Color was stored.

- 6. Load Destination Address Register to point to an area of off-screen memory.

- 7. Load Pattern Wrap Register with 02 (4-by-1 wrap).

- 8. Load Source Wrap Register with 02 (4-by-1 wrap).

- 9. Load Foreground ROP Register with CC (SRCCOPY).

- 10. Load Background ROP Register with F0 (PATCOPY).

- 11. Perform the BitBLT.

The resultant map in off-screen memory is a color-expanded version of the MixMap.

#### BitBLT #2

- 1. Program Data Routing for Screen-to-Screen operation.

- 2. Write BitMask (00001111) to off-screen memory (replicated to fill a doubleword).

- 3. Load Foreground ROP Register with CA.

- 4. Load Source Address Register with off-screen address where previous BitBLT Destination Map is stored.

- 5. Load Destination Address Register with on-screen address of the actual Pixel Map that we wish to operate on.

- 6. Perform the BitBLT.

The resultant map will have the Foreground Color in the bottom nibble of every byte for which the MixMap had a corresponding bit value of "1", and have the Background Color in the bottom nibble of every byte for which the MixMap had a corresponding bit value of "0".

The upper nibble of each byte will be unmodified.

## **Contents**

| 1. INTRODUCTION                               | 1  |

|-----------------------------------------------|----|

| 1.1 ET4000/W32i Specifications                | 2  |

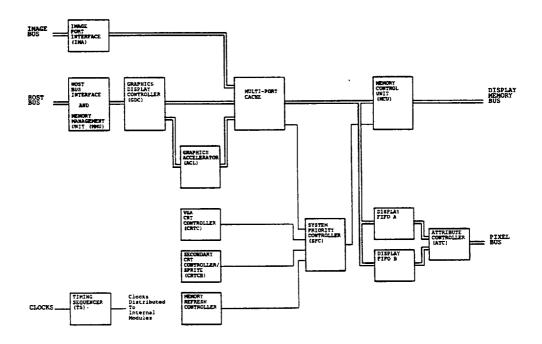

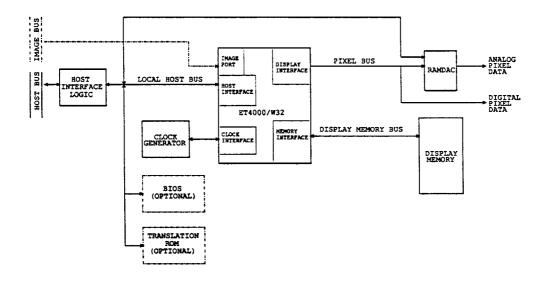

| 1.2 ET4000/W32i Overview                      | 4  |

| 1.3 Notational Conventions                    | 5  |

| 2. ET4000/W32i FUNCTIONAL DESCRIPTION         | 7  |

| 2.1 VGA CRT Controller (CRTC)                 | 8  |

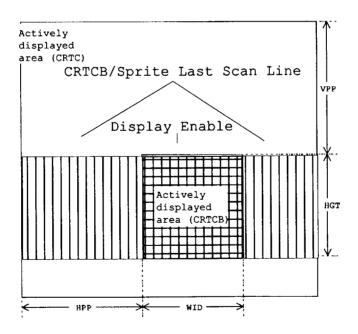

| 2.2 Secondary CRT Controller (CRTCB)/Sprite   | 9  |

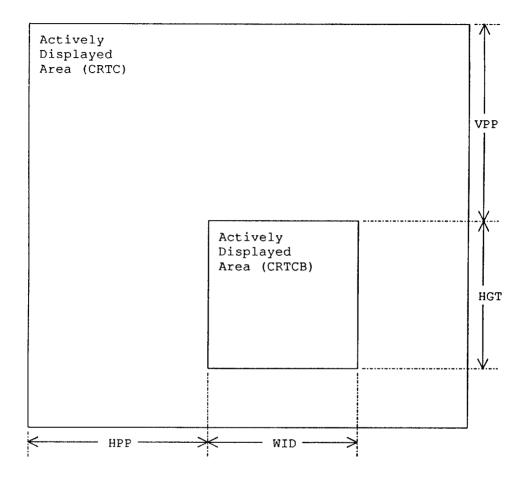

| 2.2.1 CRTCB Overview                          | 9  |

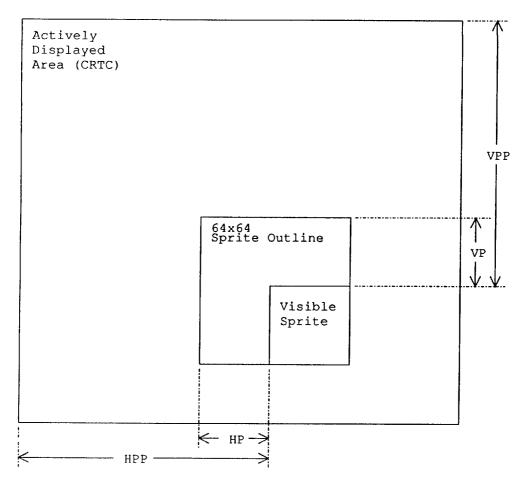

| 2.2.2 Positioning the CRTCB Window            | 9  |

| 2.2.3 CRTCB Data Format                       | 11 |

| 2.2.4 Sprite Overview                         | 11 |

| 2.2.5 Positioning the Sprite                  | 11 |

| 2.2.6 Sprite Data Format                      | 13 |

| 2.3 Memory Control Unit (MCU)                 | 13 |

| 2.3.1 Memory Interleave                       | 13 |

| 2.4 System Priority Controller (SPC)          | 14 |

| 2.5 Multiport Cache                           | 14 |

| 2.6 Timing Sequencer (TS)                     | 14 |

| 2.7 Graphics Display Controller (GDC)         | 14 |

| 2.8 Attribute Controller (ATC)                | 15 |

| 2.9 Image Port (IMA)                          | 15 |

| 2.9.1 Image Port Interface Protocol           | 16 |

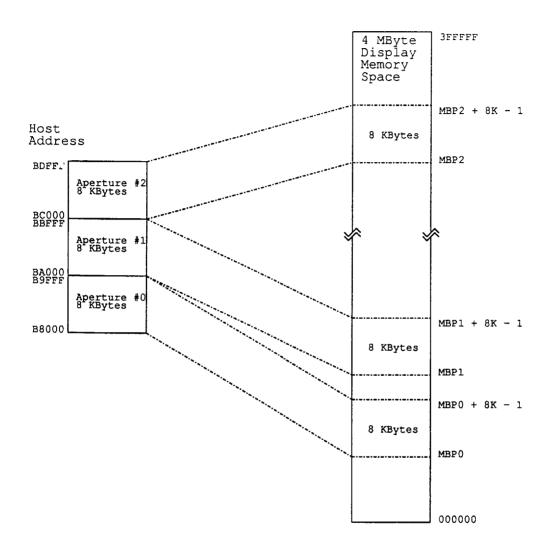

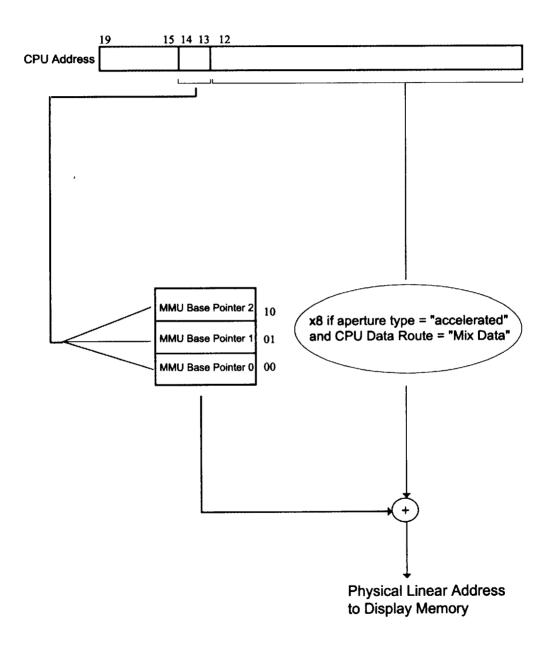

| 2.10 Memory Management Unit (MMU)             | 17 |

| 2.10.1 Software Considerations                | 17 |

| 2.10.2 Hardware Considerations                | 20 |

| 2.11 Graphics Accelerator (ACL)               | 20 |

| 2.11.1 Overview                               | 21 |

| 2.11.2 Starting an Accelerator Operation      | 22 |

| 2.11.3 The Accelerator's Queue                | 23 |

| 2.11.4 Accelerator Operation                  | 24 |

| 2.11.5 Passing Map Data to the Accelerator    | 25 |

| 2.11.5.1 Virtual Bus Size                     | 25 |

| 2.11.5.2 Synchronization                      | 26 |

| 2.11.5.3 Data Alignment                       | 27 |

| 2.11.6 Support for Common Graphics Operations | 27 |

| 2.11.6.1 Line Drawing                         | 27 |

| 2.11.6.2 Tiled and Fixed-Color Fills          | 28 |

| 2.11.6.3 Color Expansion                      | 28 |

| 2.11.6.4 Clipping                             | 28 |

| 2.11.7 Accelerator Interrupts                 | 29 |

| 2.11.8 Accelerator State Save/Restore         | 29 |

21 \_\_\_\_\_\_

CONTENTS ET4000/W32

| 2.11.8.1 State-Save Interrupt Handler                   | 30 |

|---------------------------------------------------------|----|

| 2.11.8.2 State-Restore Interrupt Handler                | 30 |

| 3. ET4000/W32i Pin Descriptions                         | 31 |

| 3.1 Power On Reset Initialize (PORI)                    | 31 |

| 3.2 Bus Configurations                                  | 32 |

| 3.3 Host Interface                                      | 33 |

| 3.3.1 ISA Bus                                           | 33 |

| 3.3.1.1 ISA POR!                                        | 33 |

| 3.3.1.2 ISA Bus Interface                               | 33 |

| 3.3.2 MCA Bus                                           | 36 |

| 3.3.2.1 MCA PORI                                        | 36 |

| 3.3.2.2 MCA Bus Interface                               | 36 |

| 3.3.3 Local Bus                                         | 38 |

| 3.3.3.1 Local Bus PORI                                  | 38 |

| 3.3.3.2 Local Bus SX/DX 16-bit Interface                | 41 |

| 3.3.3.3 Local Bus DX 32-bit Interface                   | 43 |

| 3.4 Clock Interface                                     | 45 |

| 3.5 General Interface                                   | 45 |

| 3.6 Display Memory Interface                            | 46 |

| 3.6.1 Banl: A (MD<15:0>)                                | 46 |

| 3.6.2 Bank B (MD<31:16>)                                | 46 |

| 3.7 Display Interface                                   | 47 |

| 3.7.1 Hardware Sprite                                   | 47 |

| 3.7.2 Token Status                                      | 48 |

| 3.8 Image Port Interface                                | 49 |

| 3.9 Power Source Interface                              | 50 |

| 3.10 Electrical Specifications                          | 51 |

| 3.10.1 Electrical Characteristics                       | 51 |

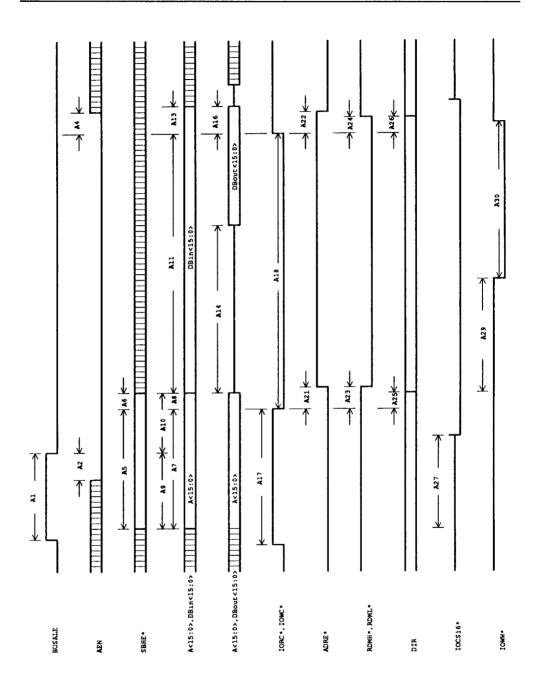

| 4. ET4000/W32i Timing Specifications                    | 53 |

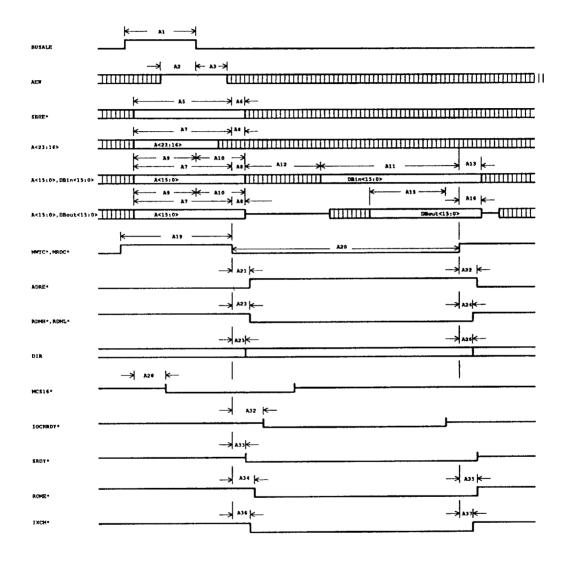

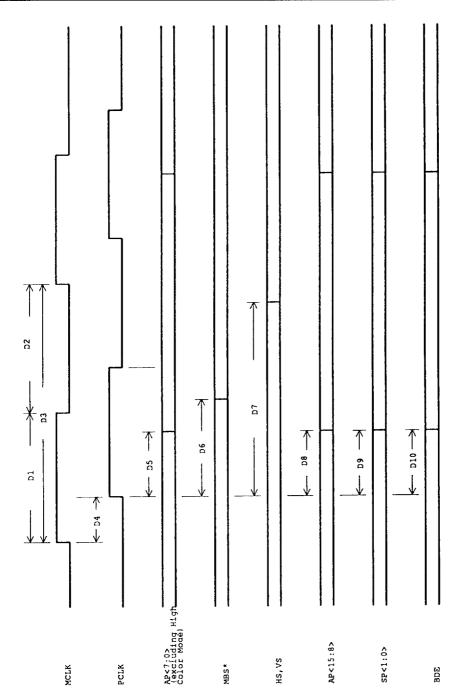

| 4.1 ISA Bus Timing                                      | 53 |

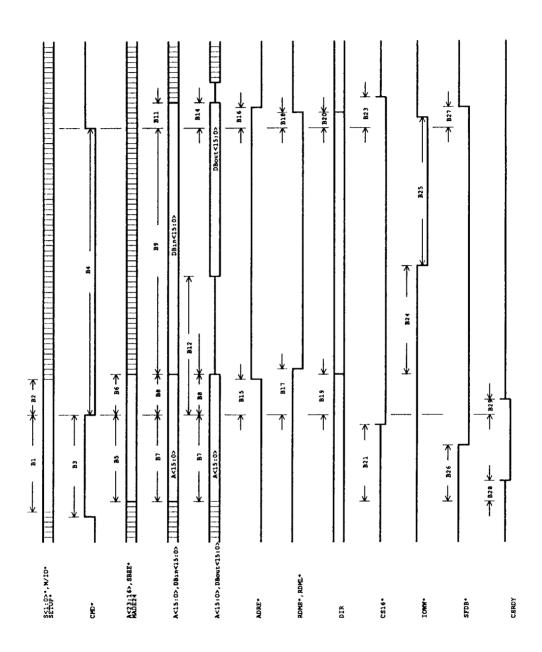

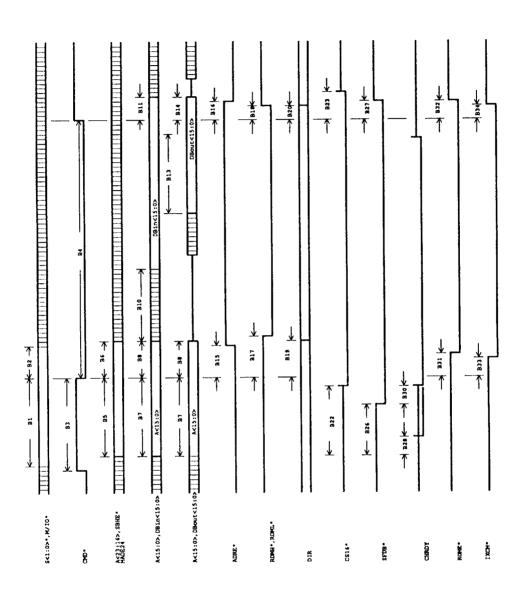

| 4.2 Micro Channel Bus Timing                            | 54 |

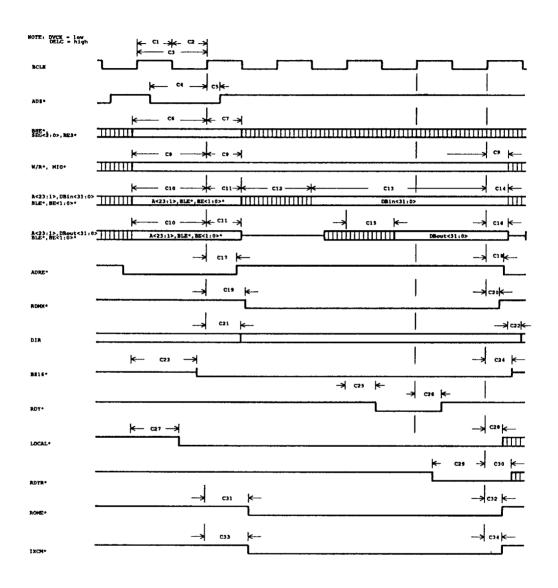

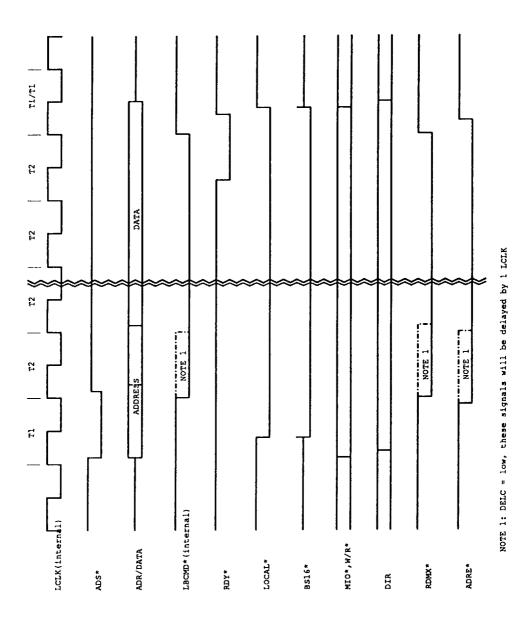

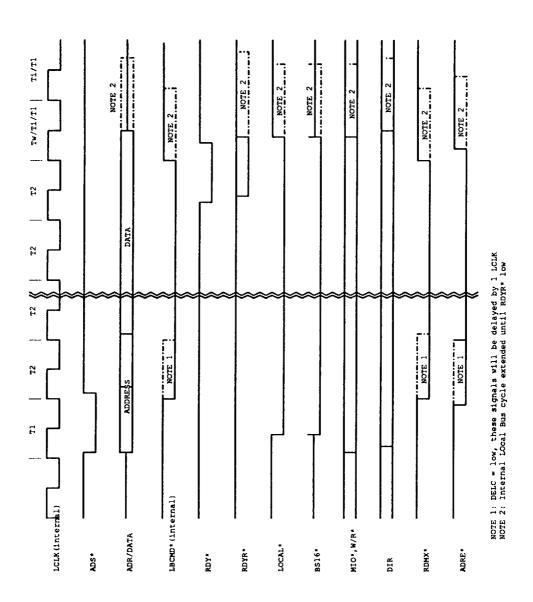

| 4.3 Local Bus Timing                                    | 55 |

| 4.4 Video Bus Interface                                 | 56 |

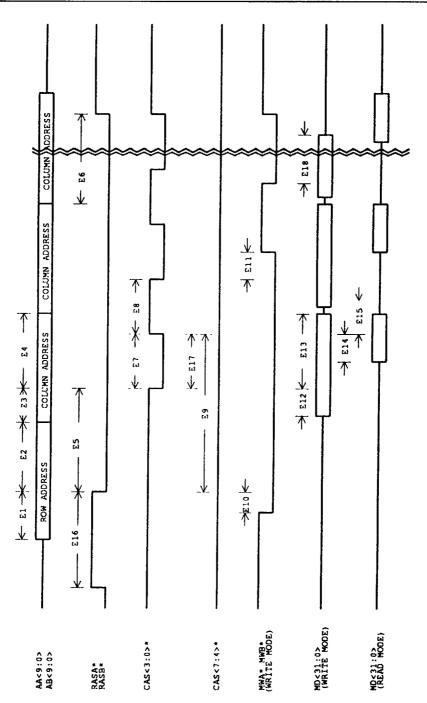

| 4.5 Display Memory Timing - Non-interleaved             | 56 |

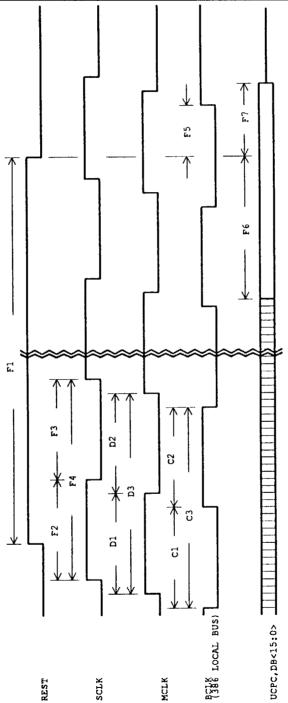

| 4.6 Clock Interface (Reset initialize and Clock Timing) | 57 |

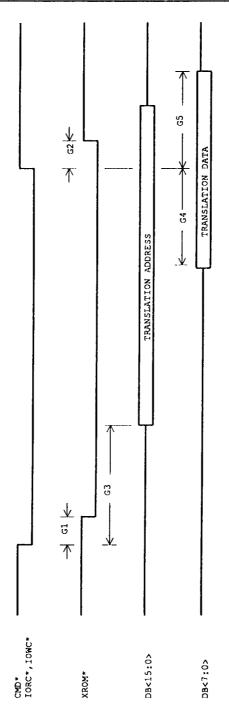

| 4.7 Translation ROM Interface                           | 57 |

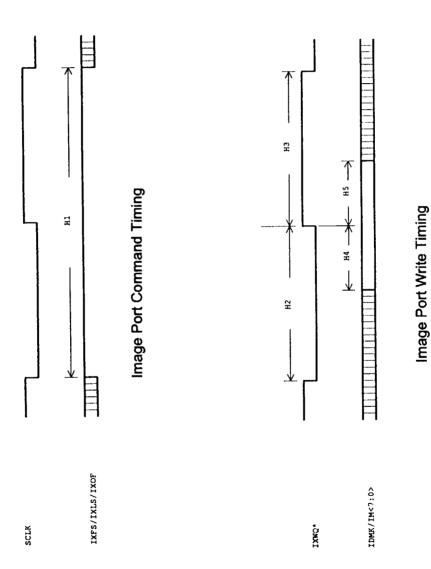

| 4.8 Image Port Timing                                   | 57 |

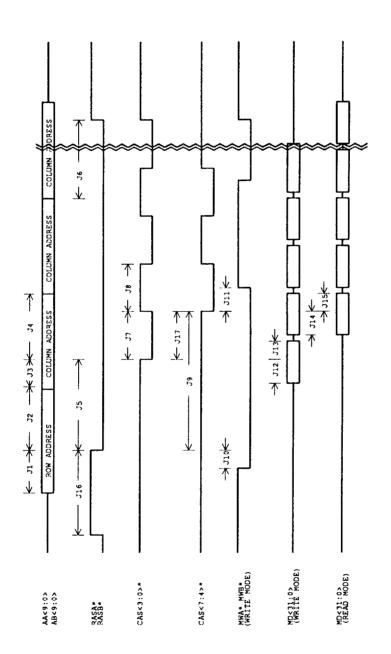

| 4.9 Display Memory Timing - Interleaved                 | 58 |

| 4.10 Timing Diagrams                                    | 59 |

| 4.11 Functional Diagrams                                | 71 |

| 5. ET4000/W32i Register Descriptions                    | 75 |

| 5.1 General Registers                                   | 77 |

| 5.1.1 Miscellaneous Output Register                     | 77 |

| 5.1.2 Input Status Register Zero                        | 80 |

| 5.1.3 Input Status Register One                         | 81 |

| 5.1.4 Feature Control Register                          | 82 |

ET4000/W32i CONTENTS

<u> V7</u>

| G ,                                                          |     |

|--------------------------------------------------------------|-----|

| 5.1.5 Video Subsystem Enable Register                        | 82  |

| 5.1.6 Display Mode Control Register                          | 83  |

| 5.1.7 Hercules Compatibility Register                        | 83  |

| 5.2 CRTC Register Description                                | 84  |

| 5.2.1 CRTC Index                                             | 87  |

| 5.2.2 CRTC Indexed Registers                                 | 88  |

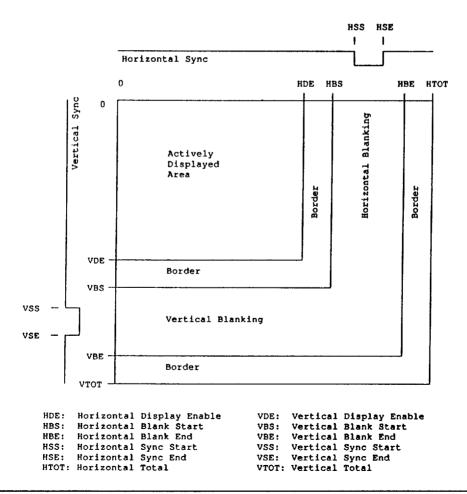

| 5.2.3 CRTC Indexed Register 0: Horizontal Total              | 88  |

| 5.2.4 CRTC Indexed Register 1: Horizontal Display End        | 88  |

| 5.2.5 CRTC Indexed Register 2: Horizontal Blank Start        | 89  |

| 5.2.6 CRTC Indexed Register 3: Horizontal Blank End          | 89  |

| 5.2.7 CRTC Indexed Register 4: Horizontal Sync Start         | 90  |

| 5.2.8 CRTC Indexed Register 5: Horizontal Sync End           | 90  |

| 5.2.9 CRTC Indexed Register 6: Vertical Total                | 91  |

| 5.2.10 CRTC Indexed Register 7: Overflow Low                 | 91  |

| 5.2.11 CRTC Indexed Register 8:                              |     |

| Preset Row Scan/Initial Row Address                          | 92  |

| 5.2.12 CRTC Indexed Register 9: Maximum Row Address          | 92  |

| 5.2.13 CRTC Indexed Register A: Cursor Start Row Address     | 93  |

| 5.2.14 CRTC Indexed Register B: Cursor End Row Address       | 93  |

| 5.2.15 CRTC Indexed Register C:                              |     |

| Linear Starting Address Middle                               | 94  |

| 5.2.16 CRTC Indexed Register D:                              |     |

| Linear Starting Address Low                                  | 94  |

| 5.2.17 CRTC Indexed Register E: Cursor Address Middle        | 95  |

| 5.2.18 CRTC Indexed Register F: Cursor Address Low           | 95  |

| 5.2.19 CRTC Indexed Register 10: Vertical Sync Start         | 96  |

| 5.2.20 CRTC Indexed Register 11: Vertical Sync End           | 97  |

| 5.2.21 CRTC Indexed Register 12: Vertical Display End        | 98  |

| 5.2.22 CRTC Indexed Register 13: Row Offset                  | 98  |

| 5.2.23 CRTC Indexed Register 14: Underline Row Address       | 99  |

| 5.2.24 CRTC Indexed Register 15: Vertical Blank Start        | 99  |

| 5.2.25 CRTC Indexed Register 16: Vertical Blank End          | 100 |

| 5.2.26 CRTC Indexed Register 17: CRTC Mode                   | 100 |

| 5.2.27 CRTC Indexed Register 18: Line Compare (Split Screen) | 103 |

| 5.2.28 CRTC Indexed Register 30:                             |     |

| System Segment Map Comparator                                | 104 |

| 5.2.29 CRTC Indexed Register 31: General Purpose             | 105 |

| 5.2.30 CRTC Indexed Register 32: RAS/CAS Configuration       | 106 |

| 5.2.31 CRTC Indexed Register 33: Extended Start Address      | 107 |

| 5.2.32 CRTC Indexed Register 34: Auxiliary Control Register  | 108 |

| 5.2.33 CRTC Indexed Register 35: Overflow High               | 109 |

| 5.2.34 CRTC Indexed Register 36:                             |     |

| Video System Configuration 1                                 | 110 |

| 5.2.35 CRTC Indexed Register 37:                             |     |

| Video System Configuration 2                                 | 112 |

| 5.2.36 CRTC Indexed Register 3F: Horizontal Overflow         | 114 |

| 5.3.1 TS Index         115           5.3.1 TS Index         115           5.3.2 TS Indexed Registers         116           5.3.3 TS Indexed Register 0: Synchronous Reset         116           5.3.4 TS Indexed Register 1: TS Mode         117           5.3.5 TS Indexed Register 2: Write Plane Mask         118           5.3.6 TS Indexed Register 3: Font Select         119           5.3.7 TS Indexed Register 4: Memory Mode         120           5.3.8 TS Indexed Register 6: TS State Control         121           5.3.9 TS Indexed Register 7: TS Auxiliary Mode         122           5.4 GDC Register Descriptions         123           5.4.1 GDC Segment Select         124           5.4.2 GDC Index         124           5.4.3 GDC Indexed Register 7: TS Auxiliary Mode         122           5.4 GDC Segment Select         124           5.4.2 GDC Index         124           5.4.3 GDC Indexed Register 8: Elect         125           5.4.5 GDC Indexed Register 9: Set/Reset         125           5.4.5 GDC Indexed Register 1: Enable Set/Reset         125           5.4.5 GDC Indexed Register 1: Enable Set/Reset         125           5.4.6 GDC Indexed Register 5: GDC Mode         128           5.4.10 GDC Indexed Register 7: Color Care         130 <t< th=""><th>_</th><th></th><th></th></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | _ |                                                               |     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---------------------------------------------------------------|-----|

| 5.3.1 TS Index       115         5.3.2 TS Indexed Registers       116         5.3.3 TS Indexed Register 0: Synchronous Reset       116         5.3.4 TS Indexed Register 1: TS Mode       117         5.3.5 TS Indexed Register 2: Write Plane Mask       118         5.3.6 TS Indexed Register 4: Memory Mode       120         5.3.7 TS Indexed Register 6: TS State Control       121         5.3.9 TS Indexed Register 7: TS Auxiliary Mode       122         5.4 GDC Register Descriptions       123         5.4.1 GDC Segment Select       124         5.4.2 GDC Index       124         5.4.3 GDC Indexed Registers       125         5.4.4 GDC Indexed Register 0: Set/Reset       125         5.4.5 GDC Indexed Register 1: Enable Set/Reset       125         5.4.6 GDC Indexed Register 3: Data Rotate and Function Select       127         5.4.8 GDC Indexed Register 4: Read Plane Select       128         5.4.9 GDC Indexed Register 6: Miscellaneous       130         5.4.10 GDC Indexed Register 7: Color Care       130         5.4.10 GDC Indexed Register 8: Bit Mask       131         5.5 ATC Register Descriptions       132         5.5.1 ATC Indexed Register 10: Mode Control       135         5.5.2 ATC Indexed Register 10: Mode Control       136         5.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   | 5.3 TS Register Descriptions                                  | 115 |

| 5.3.2 TS Indexed Register 0: Synchronous Reset       116         5.3.3 TS Indexed Register 0: Synchronous Reset       116         5.3.4 TS Indexed Register 1: TS Mode       117         5.3.5 TS Indexed Register 3: Font Select       119         5.3.6 TS Indexed Register 4: Memory Mode       120         5.3.8 TS Indexed Register 6: TS State Control       121         5.3.9 TS Indexed Register 7: TS Auxiliary Mode       122         5.4 GDC Register Descriptions       123         5.4.1 GDC Segment Select       124         5.4.2 GDC Index       124         5.4.3 GDC Indexed Registers       125         5.4.4 GDC Indexed Register 1: Enable Set/Reset       125         5.4.5 GDC Indexed Register 1: Enable Set/Reset       125         5.4.6 GDC Indexed Register 2: Color Compare       126         5.4.7 GDC Indexed Register 3: Data Rotate and Function Select       127         5.4.8 GDC Indexed Register 6: Miscellaneous       120         5.4.10 GDC Indexed Register 6: Miscellaneous       130         5.4.11 GDC Indexed Register 7: Color Care       130         5.4.12 GDC Indexed Register 8: Bit Mask       131         5.5 ATC Indexed Register 10: Mode Control       135         5.5.1 ATC Indexed Register 10: Mode Control       135         5.5.5 ATC Indexed Register 10: Mode Cont                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   |                                                               | 115 |

| 5.3.3 TS Indexed Register 0: Synchronous Reset         116           5.3.4 TS Indexed Register 1: TS Mode         117           5.3.5 TS Indexed Register 2: Write Plane Mask         118           5.3.6 TS Indexed Register 3: Font Select         119           5.3.7 TS Indexed Register 4: Memory Mode         120           5.3.8 TS Indexed Register 6: TS State Control         121           5.3.9 TS Indexed Register 7: TS Auxiliary Mode         122           5.4 GDC Register Descriptions         123           5.4.1 GDC Segment Select         124           5.4.2 GDC Indexed Registers         125           5.4.3 GDC Indexed Register 0: Set/Reset         125           5.4.5 GDC Indexed Register 1: Enable Set/Reset         125           5.4.5 GDC Indexed Register 2: Color Compare         126           5.4.7 GDC Indexed Register 3: Data Rotate and Function Select         127           5.4.8 GDC Indexed Register 4: Read Plane Select         128           5.4.9 GDC Indexed Register 6: Miscellaneous         130           5.4.10 GDC Indexed Register 6: Miscellaneous         130           5.4.12 GDC Indexed Register 6: Miscellaneous         130           5.5.1 ATC Indexed Register 13: Morizontal Pixel Panning         132           5.5.1 ATC Indexed Register 13: Morizontal Pixel Panning         135           5.5.5 AT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   |                                                               | 116 |

| 5.3.4 TS Indexed Register 1: TS Mode       117         5.3.5 TS Indexed Register 2: Write Plane Mask       118         5.3.6 TS Indexed Register 3: Font Select       119         5.3.7 TS Indexed Register 4: Memory Mode       120         5.3.8 TS Indexed Register 6: TS State Control       121         5.3.9 TS Indexed Register 7: TS Auxiliary Mode       122         5.4 GDC Register Descriptions       123         5.4.1 GDC Segment Select       124         5.4.2 GDC Index       124         5.4.3 GDC Indexed Registers       125         5.4.4 GDC Indexed Register 0: Set/Reset       125         5.4.5 GDC Indexed Register 1: Enable Set/Reset       125         5.4.5 GDC Indexed Register 2: Color Compare       126         5.4.7 GDC Indexed Register 3: Data Rotate and Function Select       127         5.4.8 GDC Indexed Register 5: GDC Mode       128         5.4.9 GDC Indexed Register 5: GDC Mode       128         5.4.10 GDC Indexed Register 6: Miscellaneous       130         5.4.11 GDC Indexed Register 7: Color Care       130         5.4.12 GDC Indexed Register 8: Bit Mask       131         5.5 ATC Indexed Register 10: Mode Control       135         5.5.1 ATC Indexed Register 10: Mode Control       135         5.5.5 ATC Indexed Register 12: Color Plane Enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |                                                               | 116 |

| 5.3.5 TS Indexed Register 2: Write Plane Mask       118         5.3.6 TS Indexed Register 3: Font Select       119         5.3.7 TS Indexed Register 4: Memory Mode       120         5.3.8 TS Indexed Register 6: TS State Control       121         5.3.9 TS Indexed Register 7: TS Auxiliary Mode       122         5.4 GDC Register Descriptions       123         5.4.1 GDC Segment Select       124         5.4.2 GDC Index       124         5.4.3 GDC Indexed Registers       125         5.4.4 GDC Indexed Register 0: Set/Reset       125         5.4.5 GDC Indexed Register 1: Enable Set/Reset       125         5.4.5 GDC Indexed Register 2: Color Compare       126         5.4.7 GDC Indexed Register 3: Data Rotate and Function Select       127         5.4.8 GDC Indexed Register 3: Data Rotate and Function Select       128         5.4.9 GDC Indexed Register 6: Miscellaneous       130         5.4.10 GDC Indexed Register 6: Miscellaneous       130         5.4.11 GDC Indexed Register 8: Bit Mask       131         5.5 ATC Register Descriptions       132         5.5.1 ATC Index       133         5.5.2 ATC Indexed Register 10: Mode Control       135         5.5.5 ATC Indexed Register 11: Overscan Color       136         5.5.6 ATC Indexed Register 12: Color Plane Enable       <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   |                                                               |     |

| 5.3.6 TS Indexed Register 3: Font Select       119         5.3.7 TS Indexed Register 4: Memory Mode       120         5.3.8 TS Indexed Register 6: TS State Control       121         5.3.9 TS Indexed Register 7: TS Auxiliary Mode       122         5.4 GDC Register Descriptions       123         5.4.1 GDC Segment Select       124         5.4.2 GDC Index       124         5.4.3 GDC Indexed Registers       125         5.4.4 GDC Indexed Register 0: Set/Reset       125         5.4.5 GDC Indexed Register 1: Enable Set/Reset       125         5.4.6 GDC Indexed Register 2: Color Compare       126         5.4.7 GDC Indexed Register 3: Data Rotate and Function Select       127         5.4.8 GDC Indexed Register 6: Miscellaneous       128         5.4.9 GDC Indexed Register 6: Miscellaneous       130         5.4.10 GDC Indexed Register 7: Color Care       130         5.4.11 GDC Indexed Register 8: Bit Mask       131         5.5 ATC Register Descriptions       132         5.5.1 ATC Index       133         5.5.2 ATC Indexed Register 10: Mode Control       135         5.5.3 ATC Indexed Register 11: Overscan Color       136         5.5.5 ATC Indexed Register 12: Color Plane Enable       137         5.5.7 ATC Indexed Register 14: Color Select       138                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   |                                                               |     |

| 5.3.7 TS Indexed Register 4: Memory Mode       120         5.3.8 TS Indexed Register 6: TS State Control       121         5.3.9 TS Indexed Register 7: TS Auxiliary Mode       122         5.4 GDC Register Descriptions       123         5.4.1 GDC Segment Select       124         5.4.2 GDC Index       124         5.4.3 GDC Indexed Registers       125         5.4.4 GDC Indexed Register 0: Set/Reset       125         5.4.5 GDC Indexed Register 1: Enable Set/Reset       125         5.4.6 GDC Indexed Register 2: Color Compare       126         5.4.7 GDC Indexed Register 3: Data Rotate and Function Select       127         5.4.8 GDC Indexed Register 5: GDC Mode       128         5.4.9 GDC Indexed Register 5: GDC Mode       128         5.4.10 GDC Indexed Register 7: Color Care       130         5.4.11 GDC Indexed Register 8: Bit Mask       131         5.5 ATC Register Descriptions       132         5.5.1 ATC Index       133         5.5.2 ATC Indexed Registers       133         5.5.3 ATC Indexed Register 10: Mode Control       135         5.5.5 ATC Indexed Register 11: Overscan Color       136         5.5.6 ATC Indexed Register 13: Horizontal Pixel Panning       137         5.5.5 ATC Indexed Register 16: Miscellaneous       138 <t< td=""><td></td><td>——————————————————————————————————————</td><td></td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   | ——————————————————————————————————————                        |     |

| 5.3.8 TS Indexed Register 6: TS State Control       121         5.3.9 TS Indexed Register 7: TS Auxiliary Mode       122         5.4.1 GDC Register Descriptions       123         5.4.1 GDC Segment Select       124         5.4.2 GDC Index       124         5.4.3 GDC Indexed Register S       125         5.4.4 GDC Indexed Register 0: Set/Reset       125         5.4.5 GDC Indexed Register 1: Enable Set/Reset       125         5.4.6 GDC Indexed Register 2: Color Compare       126         5.4.7 GDC Indexed Register 3: Data Rotate and Function Select       127         5.4.8 GDC Indexed Register 3: DC Mode       128         5.4.9 GDC Indexed Register 5: GDC Mode       128         5.4.10 GDC Indexed Register 7: Color Care       130         5.4.11 GDC Indexed Register 8: Bit Mask       131         5.5 ATC Register Descriptions       132         5.5.1 ATC Index       133         5.5.2 ATC Indexed Registers       133         5.5.3 ATC Indexed Register 10: Mode Control       135         5.5.5 ATC Indexed Register 11: Overscan Color       136         5.5.5 ATC Indexed Register 12: Color Plane Enable       137         5.5.7 ATC Indexed Register 14: Color Select       138         5.5.9 ATC Indexed Register 14: Color Select       138                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |                                                               |     |

| 5.3.9 TS Indexed Register 7: TS Auxiliary Mode         122           5.4 GDC Register Descriptions         123           5.4.1 GDC Segment Select         124           5.4.2 GDC Index         124           5.4.3 GDC Indexed Registers         125           5.4.4 GDC Indexed Register 0: Set/Reset         125           5.4.5 GDC Indexed Register 1: Enable Set/Reset         125           5.4.6 GDC Indexed Register 2: Color Compare         126           5.4.7 GDC Indexed Register 2: Dolor Compare         126           5.4.7 GDC Indexed Register 3: Data Rotate and Function Select         127           5.4.8 GDC Indexed Register 4: Read Plane Select         128           5.4.9 GDC Indexed Register 5: GDC Mode         128           5.4.9 GDC Indexed Register 6: Miscellaneous         130           5.4.11 GDC Indexed Register 7: Color Care         130           5.4.12 GDC Indexed Register 8: Bit Mask         131           5.5 ATC Register Descriptions         132           5.5.1 ATC Index         133           5.5.2 ATC Indexed Registers         133           5.5.3 ATC Indexed Register 10: Mode Control         135           5.5.5 ATC Indexed Register 11: Overscan Color         136           5.5.6 ATC Indexed Register 13: Horizontal Pixel Panning         137           5.5.9 ATC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   |                                                               |     |

| 5.4 GDC Register Descriptions       123         5.4.1 GDC Segment Select       124         5.4.2 GDC Index       124         5.4.3 GDC Indexed Registers       125         5.4.4 GDC Indexed Register 0: Set/Reset       125         5.4.5 GDC Indexed Register 1: Enable Set/Reset       125         5.4.6 GDC Indexed Register 2: Color Compare       126         5.4.7 GDC Indexed Register 3: Data Rotate and Function Select       127         5.4.8 GDC Indexed Register 5: GDC Mode       128         5.4.9 GDC Indexed Register 5: GDC Mode       128         5.4.10 GDC Indexed Register 6: Miscellaneous       130         5.4.11 GDC Indexed Register 7: Color Care       130         5.4.12 GDC Indexed Register 8: Bit Mask       131         5.5 ATC Register Descriptions       132         5.5.1 ATC Indexed Registers       133         5.5.2 ATC Indexed Registers       133         5.5.3 ATC Indexed Register 10: Mode Control       135         5.5.5 ATC Indexed Register 11: Overscan Color       136         5.5.6 ATC Indexed Register 12: Color Plane Enable       137         5.5.7 ATC Indexed Register 14: Color Select       138         5.5.9 ATC Indexed Register 14: Color Select       138         5.5.9 ATC Indexed Register 16: Miscellaneous       13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |                                                               |     |

| 5.4.1 GDC Segment Select       124         5.4.2 GDC Index       124         5.4.3 GDC Indexed Registers       125         5.4.4 GDC Indexed Register 0: Set/Reset       125         5.4.5 GDC Indexed Register 1: Enable Set/Reset       125         5.4.6 GDC Indexed Register 2: Color Compare       126         5.4.7 GDC Indexed Register 3: Data Rotate and Function Select       127         5.4.8 GDC Indexed Register 4: Read Plane Select       128         5.4.9 GDC Indexed Register 5: GDC Mode       128         5.4.10 GDC Indexed Register 6: Miscellaneous       130         5.4.11 GDC Indexed Register 7: Color Care       130         5.4.12 GDC Indexed Register 8: Bit Mask       131         5.5 ATC Register Descriptions       132         5.5.1 ATC Index       133         5.5.2 ATC Indexed Registers       133         5.5.3 ATC Indexed Registers       133         5.5.5 ATC Indexed Register 10: Mode Control       135         5.5.5 ATC Indexed Register 11: Overscan Color       136         5.5.6 ATC Indexed Register 12: Color Plane Enable       137         5.5.7 ATC Indexed Register 14: Color Select       138         5.5.9 ATC Indexed Register 16: Miscellaneous       138         5.5.10 ATC Indexed Register 16: Miscellaneous       138                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   |                                                               |     |

| 5.4.2 GDC Index       124         5.4.3 GDC Indexed Registers       125         5.4.4 GDC Indexed Register 0: Set/Reset       125         5.4.5 GDC Indexed Register 1: Enable Set/Reset       125         5.4.6 GDC Indexed Register 2: Color Compare       126         5.4.7 GDC Indexed Register 3: Data Rotate and Function Select       127         5.4.8 GDC Indexed Register 4: Read Plane Select       128         5.4.9 GDC Indexed Register 5: GDC Mode       128         5.4.10 GDC Indexed Register 6: Miscellaneous       130         5.4.11 GDC Indexed Register 7: Color Care       130         5.4.12 GDC Indexed Register 8: Bit Mask       131         5.5 ATC Register Descriptions       132         5.5.1 ATC Index       133         5.5.2 ATC Indexed Registers       133         5.5.3 ATC Indexed Registers       133         5.5.5 ATC Indexed Register 11: Overscan Color       136         5.5.5 ATC Indexed Register 12: Color Plane Enable       137         5.5.7 ATC Indexed Register 13: Horizontal Pixel Panning       137         5.5.8 ATC Indexed Register 14: Color Select       138         5.5.9 ATC Indexed Register 16: Miscellaneous       138         5.5.10 ATC Indexed Register       141         5.6.2 CRTCB/Sprite Horizontal Pixel Position Low (Index: E0)       142<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   |                                                               |     |

| 5.4.3 GDC Indexed Registers       125         5.4.4 GDC Indexed Register 0: Set/Reset       125         5.4.5 GDC Indexed Register 1: Enable Set/Reset       125         5.4.6 GDC Indexed Register 3: Data Rotate and Function Select       126         5.4.7 GDC Indexed Register 3: Data Rotate and Function Select       127         5.4.8 GDC Indexed Register 4: Read Plane Select       128         5.4.9 GDC Indexed Register 5: GDC Mode       128         5.4.10 GDC Indexed Register 6: Miscellaneous       130         5.4.11 GDC Indexed Register 7: Color Care       130         5.4.12 GDC Indexed Register 8: Bit Mask       131         5.5 ATC Register Descriptions       132         5.5.1 ATC Index       133         5.5.2 ATC Indexed Registers       133         5.5.3 ATC Indexed Registers 0-F: Palette RAM       134         5.5.4 ATC Indexed Register 10: Mode Control       135         5.5.5 ATC Indexed Register 11: Overscan Color       136         5.5.7 ATC Indexed Register 12: Color Plane Enable       137         5.5.8 ATC Indexed Register 13: Horizontal Pixel Panning       137         5.5.9 ATC Indexed Register 16: Miscellaneous       138         5.5.9 ATC Indexed Register 17: Miscellaneous       138         5.5.1 CRTCB/Sprite Register Descriptions       141         5.6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   |                                                               |     |

| 5.4.4 GDC Indexed Register 0: Set/Reset 5.4.5 GDC Indexed Register 1: Enable Set/Reset 5.4.6 GDC Indexed Register 2: Color Compare 5.4.7 GDC Indexed Register 3: Data Rotate and Function Select 5.4.8 GDC Indexed Register 4: Read Plane Select 5.4.9 GDC Indexed Register 5: GDC Mode 5.4.10 GDC Indexed Register 6: Miscellaneous 5.4.11 GDC Indexed Register 7: Color Care 5.4.12 GDC Indexed Register 8: Bit Mask 5.5 ATC Register Descriptions 5.5.1 ATC Indexed Registers 5.5.2 ATC Indexed Registers 5.5.3 ATC Indexed Registers 5.5.4 ATC Indexed Register 10: Mode Control 5.5.5 ATC Indexed Register 11: Overscan Color 5.5.6 ATC Indexed Register 12: Color Plane Enable 5.5.7 ATC Indexed Register 13: Horizontal Pixel Panning 5.5.8 ATC Indexed Register 16: Miscellaneous 138 5.5.9 ATC Indexed Register 16: Miscellaneous 138 5.5.10 ATC Indexed Register 17: Miscellaneous 138 5.5.10 ATC Indexed Register 17: Miscellaneous 139 5.6 CRTCB/Sprite Register Descriptions 141 5.6.1 CRTCB Index Register Position Low (Index: E0) 142 5.6.3 CRTCB/Sprite Horizontal Pixel Position Low (Index: E1) 142 5.6.4 CRTCB Width Low/Sprite Horizontal Preset (Index: E2) 143 5.6.5 CRTCB Width High (Index: E3) 15.6.8 CRTCB/Sprite Vertical Pixel Position Low (Index: E4) 15.6.9 CRTCB/Sprite Vertical Pixel Position High (Index: E5) 15.6.8 CRTCB Height Low/Sprite Vertical Preset (Index: E5) 15.6.9 CRTCB Height High (Index: E7) 145                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   |                                                               |     |

| 5.4.5 GDC Indexed Register 1: Enable Set/Reset 5.4.6 GDC Indexed Register 2: Color Compare 5.4.7 GDC Indexed Register 3: Data Rotate and Function Select 5.4.8 GDC Indexed Register 4: Read Plane Select 5.4.9 GDC Indexed Register 5: GDC Mode 5.4.10 GDC Indexed Register 6: Miscellaneous 5.4.11 GDC Indexed Register 7: Color Care 5.4.12 GDC Indexed Register 8: Bit Mask 5.5 ATC Register Descriptions 5.5.1 ATC Index 5.5.2 ATC Indexed Registers 5.5.3 ATC Indexed Registers 5.5.4 ATC Indexed Register 10: Mode Control 5.5.5 ATC Indexed Register 11: Overscan Color 5.5.6 ATC Indexed Register 12: Color Plane Enable 5.5.7 ATC Indexed Register 13: Horizontal Pixel Panning 5.5.8 ATC Indexed Register 14: Color Select 5.5.9 ATC Indexed Register 16: Miscellaneous 5.5.10 ATC Indexed Register 17: Miscellaneous 5.5.10 ATC Indexed Register 16: Miscellaneous 5.5.10 ATC Indexed Register 17: Miscellaneous 5.5.10 ATC Indexed Register 16: Miscellaneous 5.5.10 ATC Indexed Register 17: Miscellaneous 5.5.10 ATC Indexed Register 17: Miscellaneous 5.5.10 ATC Indexed Register 19: Miscellaneous 5.5.10 ATC Indexed Register 10: Miscellaneous 138 |   | <del>_</del>                                                  |     |

| 5.4.6 GDC Indexed Register 2: Color Compare 5.4.7 GDC Indexed Register 3: Data Rotate and Function Select 5.4.8 GDC Indexed Register 4: Read Plane Select 5.4.9 GDC Indexed Register 5: GDC Mode 5.4.10 GDC Indexed Register 6: Miscellaneous 5.4.11 GDC Indexed Register 7: Color Care 5.4.12 GDC Indexed Register 8: Bit Mask 5.5.1 ATC Register Descriptions 5.5.1 ATC Index 5.5.1 ATC Index 133 5.5.2 ATC Indexed Registers 5.5.3 ATC Indexed Registers 5.5.4 ATC Indexed Register 10: Mode Control 5.5.5 ATC Indexed Register 11: Overscan Color 5.5.6 ATC Indexed Register 12: Color Plane Enable 5.5.7 ATC Indexed Register 13: Horizontal Pixel Panning 5.5.8 ATC Indexed Register 14: Color Select 5.5.9 ATC Indexed Register 16: Miscellaneous 5.5.10 ATC Indexed Register 17: Miscellaneous 5.5.10 ATC Indexed Register 17: Miscellaneous 5.5.10 ATC Indexed Register 17: Miscellaneous 5.5.10 ATC Indexed Register 16: Miscellaneous 5.5.10 ATC Indexed Register 17: Miscellaneous 5.5.10 ATC Indexed Register 16: Miscellaneous 5.5.10 ATC Indexed Register 17: Miscellaneous 5.5.10 ATC Indexed Register 16: Miscellaneous 5.5.10 ATC Indexed Register 16: Miscellaneous 5.5.10 ATC Indexed Register 17: Miscellaneous 5.5.10 ATC Indexed Register 16: Miscellaneous 5.5.10 ATC Indexed Register 17: Miscellaneous 5.5.10 ATC Indexed Register 10: Miscellaneous 138 5.6.10 CRTCB/Sprite Horizontal Pixel Position Low (Index: E1) 142 15.6.20 CRTCB/Sprite Vertical Pixel Position Low (Index: E4) 143 15.6.30 CRTCB/Sprite Vertical Pixel Position Low (Index: E6) 144 15.6.90 CRTCB/Sprite Vertical Pixel Position High (Index: E6) 145 146 147                                                                              |   |                                                               |     |

| 5.4.7 GDC Indexed Register 3: Data Rotate and Function Select 5.4.8 GDC Indexed Register 4: Read Plane Select 5.4.9 GDC Indexed Register 5: GDC Mode 5.4.10 GDC Indexed Register 6: Miscellaneous 5.4.11 GDC Indexed Register 7: Color Care 5.4.12 GDC Indexed Register 8: Bit Mask 5.4.12 GDC Indexed Register 8: Bit Mask 5.5.1 ATC Register Descriptions 5.5.1 ATC Indexed Registers 5.5.1 ATC Indexed Registers 5.5.3 ATC Indexed Registers 5.5.4 ATC Indexed Registers 5.5.5 ATC Indexed Register 10: Mode Control 5.5.5 ATC Indexed Register 11: Overscan Color 5.5.6 ATC Indexed Register 12: Color Plane Enable 5.5.7 ATC Indexed Register 13: Horizontal Pixel Panning 5.5.8 ATC Indexed Register 13: Horizontal Pixel Panning 5.5.9 ATC Indexed Register 16: Miscellaneous 5.5.10 ATC Indexed Register 16: Miscellaneous 5.5.10 ATC Indexed Register 17: Miscellaneous 5.6.1 CRTCB/Sprite Register Descriptions 141 5.6.2 CRTCB/Sprite Horizontal Pixel Position Low (Index: E0) 142 5.6.3 CRTCB/Sprite Horizontal Pixel Position High (Index: E1) 5.6.4 CRTCB Width Low/Sprite Horizontal Preset (Index: E2) 5.6.5 CRTCB Width High (Index: E3) 5.6.6 CRTCB/Sprite Vertical Pixel Position Low (Index: E4) 5.6.7 CRTCB/Sprite Vertical Pixel Position Low (Index: E4) 5.6.8 CRTCB Height High (Index: E7) 5.6.10 CRTCB/Sprite Vertical Pixel Position High (Index: E5) 5.6.10 CRTCB Height High (Index: E7) 5.6.10 CRTCB/Sprite Starting Address Low Register (Index: E8)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |                                                               |     |

| 5.4.8 GDC Indexed Register 4: Read Plane Select 5.4.9 GDC Indexed Register 5: GDC Mode 128 5.4.10 GDC Indexed Register 6: Miscellaneous 130 5.4.11 GDC Indexed Register 7: Color Care 130 5.4.12 GDC Indexed Register 8: Bit Mask 131 5.5 ATC Register Descriptions 132 5.5.1 ATC Index 133 5.5.2 ATC Indexed Registers 133 5.5.3 ATC Indexed Registers 134 5.5.4 ATC Indexed Registers 0-F: Palette RAM 134 5.5.4 ATC Indexed Register 10: Mode Control 135 5.5.5 ATC Indexed Register 11: Overscan Color 136 5.5.6 ATC Indexed Register 12: Color Plane Enable 137 5.5.7 ATC Indexed Register 13: Horizontal Pixel Panning 137 5.5.8 ATC Indexed Register 14: Color Select 138 5.5.9 ATC Indexed Register 16: Miscellaneous 138 5.5.10 ATC Indexed Register 16: Miscellaneous 138 5.5.10 ATC Indexed Register 17: Miscellaneous 139 5.6 CRTCB/Sprite Register Descriptions 141 5.6.1 CRTCB Index Register 142 5.6.3 CRTCB/Sprite Horizontal Pixel Position Low (Index: E0) 142 5.6.4 CRTCB Width Low/Sprite Horizontal Preset (Index: E2) 142 5.6.5 CRTCB Width Low/Sprite Horizontal Preset (Index: E2) 143 5.6.6 CRTCB/Sprite Vertical Pixel Position Low (Index: E4) 143 5.6.7 CRTCB/Sprite Vertical Pixel Position Low (Index: E4) 143 5.6.8 CRTCB Height Low/Sprite Vertical Preset (Index: E5) 144 5.6.9 CRTCB Height High (Index: E7) 145                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   | · · · · · · · · · · · · · · · · · · ·                         |     |

| 5.4.9 GDC Indexed Register 5: GDC Mode 5.4.10 GDC Indexed Register 6: Miscellaneous 5.4.11 GDC Indexed Register 7: Color Care 130 5.4.12 GDC Indexed Register 8: Bit Mask 131 5.5 ATC Register Descriptions 132 5.5.1 ATC Index 133 5.5.2 ATC Indexed Registers 133 5.5.3 ATC Indexed Registers 134 5.5.4 ATC Indexed Registers 0-F: Palette RAM 134 5.5.4 ATC Indexed Register 10: Mode Control 135 5.5.5 ATC Indexed Register 11: Overscan Color 136 5.5.6 ATC Indexed Register 12: Color Plane Enable 137 5.5.7 ATC Indexed Register 13: Horizontal Pixel Panning 137 5.5.8 ATC Indexed Register 14: Color Select 138 5.5.9 ATC Indexed Register 16: Miscellaneous 138 5.5.10 ATC Indexed Register 17: Miscellaneous 138 5.5.10 ATC Indexed Register 17: Miscellaneous 139 5.6 CRTCB/Sprite Register Descriptions 141 5.6.1 CRTCB Index Register 15.6.2 CRTCB/Sprite Horizontal Pixel Position Low (Index: E0) 142 5.6.3 CRTCB/Sprite Horizontal Pixel Position High (Index: E1) 142 5.6.4 CRTCB Width Low/Sprite Horizontal Preset (Index: E2) 143 5.6.6 CRTCB/Sprite Vertical Pixel Position Low (Index: E4) 15.6.7 CRTCB/Sprite Vertical Pixel Position High (Index: E5) 143 5.6.8 CRTCB Height Low/Sprite Vertical Preset (Index: E6) 144 5.6.9 CRTCB Height High (Index: E7) 145                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   |                                                               |     |

| 5.4.10 GDC Indexed Register 6: Miscellaneous 5.4.11 GDC Indexed Register 7: Color Care 130 5.4.12 GDC Indexed Register 8: Bit Mask 131 5.5 ATC Register Descriptions 132 5.5.1 ATC Index 133 5.5.2 ATC Indexed Registers 133 5.5.3 ATC Indexed Registers 134 5.5.4 ATC Indexed Registers 0-F: Palette RAM 134 5.5.4 ATC Indexed Register 10: Mode Control 135 5.5.5 ATC Indexed Register 11: Overscan Color 136 5.5.6 ATC Indexed Register 12: Color Plane Enable 137 5.5.7 ATC Indexed Register 13: Horizontal Pixel Panning 137 5.5.8 ATC Indexed Register 14: Color Select 138 5.5.9 ATC Indexed Register 16: Miscellaneous 138 5.5.10 ATC Indexed Register 16: Miscellaneous 138 5.5.10 ATC Indexed Register 17: Miscellaneous 139 5.6 CRTCB/Sprite Register Descriptions 141 5.6.1 CRTCB Index Register 15.6.2 CRTCB/Sprite Horizontal Pixel Position Low (Index: E0) 142 5.6.3 CRTCB/Sprite Horizontal Pixel Position High (Index: E1) 142 5.6.4 CRTCB Width Low/Sprite Horizontal Preset (Index: E2) 143 5.6.6 CRTCB/Sprite Vertical Pixel Position Low (Index: E4) 15.6.7 CRTCB/Sprite Vertical Pixel Position High (Index: E5) 143 5.6.8 CRTCB Height Low/Sprite Vertical Preset (Index: E6) 144 5.6.9 CRTCB Height High (Index: E7) 145                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |                                                               |     |

| 5.4.11 GDC Indexed Register 7: Color Care 5.4.12 GDC Indexed Register 8: Bit Mask 131 5.5 ATC Register Descriptions 132 5.5.1 ATC Index 133 5.5.2 ATC Indexed Registers 133 5.5.3 ATC Indexed Registers 0-F: Palette RAM 134 5.5.4 ATC Indexed Register 10: Mode Control 135 5.5.5 ATC Indexed Register 11: Overscan Color 136 5.5.6 ATC Indexed Register 12: Color Plane Enable 137 5.5.7 ATC Indexed Register 13: Horizontal Pixel Panning 137 5.5.8 ATC Indexed Register 14: Color Select 138 5.5.9 ATC Indexed Register 16: Miscellaneous 138 5.5.10 ATC Indexed Register 16: Miscellaneous 139 5.6 CRTCB/Sprite Register Descriptions 141 5.6.1 CRTCB Index Register 15.6.2 CRTCB/Sprite Horizontal Pixel Position Low (Index: E0) 142 5.6.3 CRTCB/Sprite Horizontal Pixel Position High (Index: E1) 142 5.6.4 CRTCB Width Low/Sprite Horizontal Preset (Index: E2) 143 5.6.5 CRTCB/Sprite Vertical Pixel Position Low (Index: E4) 143 5.6.7 CRTCB/Sprite Vertical Pixel Position High (Index: E5) 143 5.6.8 CRTCB Height Low/Sprite Vertical Preset (Index: E6) 144 5.6.9 CRTCB Height High (Index: E7) 145                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |                                                               |     |

| 5.4.12 GDC Indexed Register 8: Bit Mask  5.5 ATC Register Descriptions  5.5.1 ATC Index  5.5.1 ATC Index  133  5.5.2 ATC Indexed Registers  133  5.5.3 ATC Indexed Registers 0-F: Palette RAM  5.5.4 ATC Indexed Register 10: Mode Control  135  5.5.5 ATC Indexed Register 11: Overscan Color  136  5.5.6 ATC Indexed Register 12: Color Plane Enable  137  5.5.7 ATC Indexed Register 13: Horizontal Pixel Panning  137  5.5.8 ATC Indexed Register 14: Color Select  138  5.5.9 ATC Indexed Register 16: Miscellaneous  138  5.5.10 ATC Indexed Register 17: Miscellaneous  139  5.6 CRTCB/Sprite Register Descriptions  141  5.6.1 CRTCB Index Register  5.6.2 CRTCB/Sprite Horizontal Pixel Position Low (Index: E0)  142  5.6.3 CRTCB/Sprite Horizontal Pixel Position High (Index: E1)  5.6.4 CRTCB Width Low/Sprite Horizontal Preset (Index: E2)  142  5.6.5 CRTCB/Sprite Vertical Pixel Position Low (Index: E4)  5.6.7 CRTCB/Sprite Vertical Pixel Position High (Index: E4)  5.6.8 CRTCB Height Low/Sprite Vertical Preset (Index: E6)  144  5.6.9 CRTCB Height High (Index: E7)  145                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |                                                               |     |

| 5.5 ATC Register Descriptions 5.5.1 ATC Index 5.5.1 ATC Index 5.5.2 ATC Indexed Registers 5.5.3 ATC Indexed Registers 0-F: Palette RAM 5.5.4 ATC Indexed Register 10: Mode Control 5.5.5 ATC Indexed Register 11: Overscan Color 5.5.6 ATC Indexed Register 12: Color Plane Enable 5.5.7 ATC Indexed Register 12: Color Plane Enable 5.5.8 ATC Indexed Register 13: Horizontal Pixel Panning 5.5.8 ATC Indexed Register 14: Color Select 138 5.5.9 ATC Indexed Register 16: Miscellaneous 138 5.5.10 ATC Indexed Register 17: Miscellaneous 139 5.6 CRTCB/Sprite Register Descriptions 141 5.6.1 CRTCB Index Register 15.6.2 CRTCB/Sprite Horizontal Pixel Position Low (Index: E0) 142 5.6.3 CRTCB/Sprite Horizontal Pixel Position High (Index: E1) 142 5.6.4 CRTCB Width Low/Sprite Horizontal Preset (Index: E2) 143 5.6.5 CRTCB/Sprite Vertical Pixel Position Low (Index: E4) 143 5.6.7 CRTCB/Sprite Vertical Pixel Position High (Index: E5) 143 5.6.8 CRTCB Height Low/Sprite Vertical Preset (Index: E6) 144 5.6.9 CRTCB Height High (Index: E7) 145                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   |                                                               |     |

| 5.5.1 ATC Index 5.5.2 ATC Indexed Registers 5.5.3 ATC Indexed Registers 0-F: Palette RAM 5.5.4 ATC Indexed Register 10: Mode Control 5.5.5 ATC Indexed Register 11: Overscan Color 136 5.5.5 ATC Indexed Register 12: Color Plane Enable 137 5.5.6 ATC Indexed Register 13: Horizontal Pixel Panning 137 5.5.8 ATC Indexed Register 14: Color Select 138 5.5.9 ATC Indexed Register 16: Miscellaneous 138 5.5.10 ATC Indexed Register 17: Miscellaneous 139 5.6 CRTCB/Sprite Register Descriptions 141 5.6.1 CRTCB Index Register 15.6.2 CRTCB/Sprite Horizontal Pixel Position Low (Index: E0) 142 5.6.3 CRTCB/Sprite Horizontal Pixel Position High (Index: E1) 142 5.6.4 CRTCB Width Low/Sprite Horizontal Preset (Index: E2) 143 5.6.6 CRTCB/Sprite Vertical Pixel Position Low (Index: E4) 143 5.6.7 CRTCB/Sprite Vertical Pixel Position High (Index: E5) 143 5.6.8 CRTCB Height Low/Sprite Vertical Preset (Index: E6) 144 5.6.9 CRTCB Height High (Index: E7) 144 5.6.10 CRTCB/Sprite Starting Address Low Register (Index: E8)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   |                                                               |     |

| 5.5.2 ATC Indexed Registers 5.5.3 ATC Indexed Registers 0-F: Palette RAM 5.5.4 ATC Indexed Register 10: Mode Control 5.5.5 ATC Indexed Register 11: Overscan Color 5.5.6 ATC Indexed Register 12: Color Plane Enable 5.5.7 ATC Indexed Register 13: Horizontal Pixel Panning 5.5.8 ATC Indexed Register 14: Color Select 138 5.5.9 ATC Indexed Register 16: Miscellaneous 138 5.5.10 ATC Indexed Register 17: Miscellaneous 139 5.6 CRTCB/Sprite Register Descriptions 141 5.6.1 CRTCB Index Register 15.6.2 CRTCB/Sprite Horizontal Pixel Position Low (Index: E0) 142 5.6.3 CRTCB/Sprite Horizontal Pixel Position High (Index: E1) 142 5.6.4 CRTCB Width Low/Sprite Horizontal Preset (Index: E2) 143 5.6.6 CRTCB/Sprite Vertical Pixel Position Low (Index: E4) 143 5.6.7 CRTCB/Sprite Vertical Pixel Position High (Index: E5) 143 5.6.8 CRTCB Height Low/Sprite Vertical Preset (Index: E6) 144 5.6.9 CRTCB Height High (Index: E7) 145                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   |                                                               |     |

| 5.5.3 ATC Indexed Registers 0-F: Palette RAM 5.5.4 ATC Indexed Register 10: Mode Control 5.5.5 ATC Indexed Register 11: Overscan Color 5.5.6 ATC Indexed Register 12: Color Plane Enable 5.5.7 ATC Indexed Register 13: Horizontal Pixel Panning 5.5.8 ATC Indexed Register 14: Color Select 138 5.5.9 ATC Indexed Register 16: Miscellaneous 138 5.5.10 ATC Indexed Register 17: Miscellaneous 139 5.6 CRTCB/Sprite Register Descriptions 141 5.6.1 CRTCB Index Register 15.6.2 CRTCB/Sprite Horizontal Pixel Position Low (Index: E0) 142 5.6.3 CRTCB/Sprite Horizontal Pixel Position High (Index: E1) 142 5.6.4 CRTCB Width Low/Sprite Horizontal Preset (Index: E2) 143 5.6.5 CRTCB/Sprite Vertical Pixel Position Low (Index: E4) 143 5.6.7 CRTCB/Sprite Vertical Pixel Position High (Index: E5) 143 5.6.8 CRTCB Height Low/Sprite Vertical Preset (Index: E6) 144 5.6.9 CRTCB Height High (Index: E7) 145                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |                                                               |     |

| 5.5.4 ATC Indexed Register 10: Mode Control 5.5.5 ATC Indexed Register 11: Overscan Color 5.5.6 ATC Indexed Register 12: Color Plane Enable 5.5.7 ATC Indexed Register 13: Horizontal Pixel Panning 5.5.8 ATC Indexed Register 14: Color Select 138 5.5.9 ATC Indexed Register 16: Miscellaneous 138 5.5.10 ATC Indexed Register 17: Miscellaneous 139 5.6 CRTCB/Sprite Register Descriptions 141 5.6.1 CRTCB Index Register 15.6.2 CRTCB/Sprite Horizontal Pixel Position Low (Index: E0) 142 5.6.3 CRTCB/Sprite Horizontal Pixel Position High (Index: E1) 142 5.6.4 CRTCB Width Low/Sprite Horizontal Preset (Index: E2) 143 5.6.5 CRTCB/Sprite Vertical Pixel Position Low (Index: E4) 143 5.6.7 CRTCB/Sprite Vertical Pixel Position High (Index: E5) 143 5.6.8 CRTCB Height Low/Sprite Vertical Preset (Index: E6) 144 5.6.9 CRTCB Height High (Index: E7) 145                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |                                                               |     |

| 5.5.5 ATC Indexed Register 11: Overscan Color 5.5.6 ATC Indexed Register 12: Color Plane Enable 137 5.5.7 ATC Indexed Register 13: Horizontal Pixel Panning 137 5.5.8 ATC Indexed Register 14: Color Select 138 5.5.9 ATC Indexed Register 16: Miscellaneous 138 5.5.10 ATC Indexed Register 17: Miscellaneous 139 5.6 CRTCB/Sprite Register Descriptions 141 5.6.1 CRTCB Index Register 15.6.2 CRTCB/Sprite Horizontal Pixel Position Low (Index: E0) 142 5.6.3 CRTCB/Sprite Horizontal Pixel Position High (Index: E1) 142 5.6.4 CRTCB Width Low/Sprite Horizontal Preset (Index: E2) 143 5.6.5 CRTCB Width High (Index: E3) 143 5.6.6 CRTCB/Sprite Vertical Pixel Position Low (Index: E4) 143 5.6.7 CRTCB/Sprite Vertical Pixel Position High (Index: E5) 143 5.6.8 CRTCB Height Low/Sprite Vertical Preset (Index: E6) 144 5.6.9 CRTCB Height High (Index: E7) 145                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   |                                                               |     |